# OPTIMIZING STENCIL DESIGN FOR LEAD-FREE SMT PROCESSING

Ranjit S Pandher

Chrys Shea

Cookson Electronics Assembly Materials

Jersey City, New Jersey, USA

#### **Abstract**

As any new technology emerges, increasing levels of refinement are required to facilitate the mainstream implementation and continual improvement processes. In the case of lead-free processing, the initial hurdles of alloy and chemistry selection are cleared on the first level, providing a base process. The understanding gained from early work on the base process leads to the next level of refinement in optimizing the primary factors that influence yield. These factors may include thermal profiles, PWB surface finishes, component metallization, solder mask selection or stencil design.

Because stencil printing has such a large influence on first pass yield, and lead-free alloys have different wetting properties than their leadbearing counterparts, the authors have undertaken a study to identify stencil aperture geometries that optimize desired characteristics. The concern of the lower spread of lead-free alloys on some alternate surface finishes is explored. Aperture designs that maximize pad coverage while minimizing defects like mid-chip solder balls are offered. In addition to aperture design guidelines, methods of optimizing the overall stencil design will be reviewed.

Key Words: Lead-Free, Stencil Printing, Aperture Design, Process Control

### Introduction

The primary goal of stencil printing is to put the proper amount of solder in the proper location repeatably. The aperture size, shape, and stencil thickness determine the amount of solder deposited, while the position of the aperture determines the location of the deposit.

Methods of effectively controlling the position of the aperture have already been determined1 and will be reviewed later in the paper. The goal of this study was to determine the best size and shape of the aperture for lead-free solder pastes.

It is generally accepted that lead-free solders do not wet or spread as readily as their lead-bearing counterparts. This behavioral difference presents concerns for assemblers on several fronts: exposed copper (or substrate surface finish) near the perimeters of pads, different defect rates for mid-chip solderballs, and tombstones.

An experiment was designed to quantify the impact of different solder spread on typical surface mount defects. Part I of the experiment baselined spread and defect rates for both lead-bearing and lead-free pastes with aperture geometries that have traditionally been used in the lead-bearing SMT process. Part II attempted to optimize stencil apertures to improve upon the defect rates when using a lead-free paste. In Part I, board surface finishes included Organic Solderability Preservative (OSP), Electroless Nickel-Immersion Gold (ENIG), Immersion Silver (ImAg) and Immersion Tin (ImSn). OSP and ImSn were used in Part II.

### **Experimental Design**

Wetting and Spread – Spread characteristics of the solder pastes can be studied by two methods. The first method involves printing a circular deposit of known area on bare metallic substrate, reflowing the sample, and measuring the area covered with solder post-reflow. The ratio of the post-reflow area to that of the original printed area gives a measure of the spreading of the paste and an indication of wetting for the particular board finish on which it was measured.

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

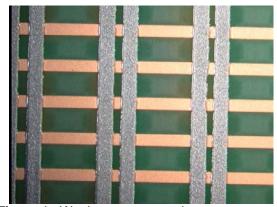

An alternative solder spread/wetting test involves printing pairs of uniform thickness (40 mil) solder paste stripes onto an array of uniform thickness (30 mil), equally spaced traces on the board. The paste stripes have increasing gap sizes between them and are printed in a direction perpendicular to that of the traces, as shown in figure. 1.

**Figure 1**. Wetting test cross print pattern.

During reflow the molten solder expands along the metal lines on the board. If there is enough spread, the gap between two adjacent solder spots is bridged. The gaps between solder paste stripes are varied from 0.1 mm to 0.8 mm. There are a maximum number of twenty bridges possible for each gap size. The number of gaps to bridge is counted and the results are plotted as a function of the gap size. A reflowed test coupon is shown in Figure 2.

Figure 2 . Wetting test cross-print post reflow

Quad Flat Packs – For devices with pitches under 20 mil (0.5mm), the risk of solder bridges is increased when the aperture to pad ratio is 1:1. To reduce the risk of solder bridges the usual trick is to reduce the print area by certain amount. A 10% reduction in aperture area, known as aperture cropping is commonly employed. However, the risk of exposed pad material is increased when printing with a 10% reduction. Although exposed pad material has not been shown to present a reliability concern, it can present a cosmetic concern for some assemblers. If exposed pads are a concern with lead-bearing paste, the concern is heightened with lead-free paste due to its lower spread characteristics.

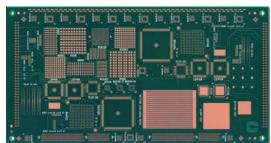

To quantify the impact of aperture cropping two, 20-mil pitch QFP's were assembled on each test vehicle. In Part I of the study, one of the QFP's had apertures at 1:1 with the pads; the other was reduced by 10%. In Part II of the study, both apertures were fixed at 1:1, 5% reduction, and 10% reduction. 5- and 6-mil foils (125 and 150 um, respectively) were used in both portions of the test. In total, four combinations of area and foil thickness were test in Part I and six combinations were tested in Part II. The test vehicle is shown in Fig 3.

**Figure 3**. Cookson Electronics Reliability and Functionality (CERF) Test Vehicle

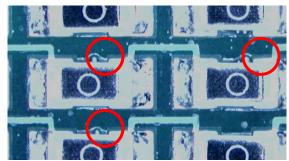

**Mid-chip solder balls** (MCSB) are also a common defect that can be impacted by stencil design. Although the formation of mid-chip balls can have many causes – including pad design, soldermask relief, placement pressure, termination geometry and metallization, pad finish and reflow profile – the size and shape of the solder deposit will positively or negatively influence the formation of mid-chip balls.

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

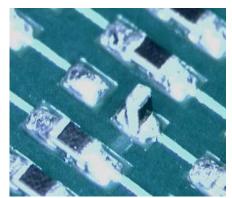

If a (relatively) larger volume of solder paste is depositied on the pad, especially in the area where the chip will be placed, the placement of the chip will displace the soft paste. Any paste that is pushed under the body of the device may pull back to the pad during the reflow cycle, or it may not. If the solder does not pull back, it migrates to the side of the device through capillary action during its liquidus phase, forming a solder ball that solidifies upon cooling. Figure. 4 shows a picture of the typical mid-chip solder balls.

Figure 4. Mid-Chip Solder Balls (MCSB's).

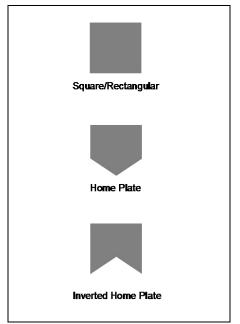

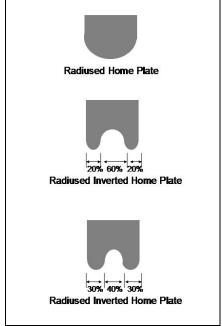

Data generated over hundreds of MCSB tests with lead-bearing paste indicates that the worst case stencil design for MCSB's is a rectangular aperture with a 1:1 pad ratio and a 6 mil stencil foil. The best case is a "homeplate" design with a 10% area reduction on a 5 mil foil. Figure 5 illustrates the rectangular, homeplate and inverse homeplate designs. The historical data also indicates that a soak profile is less forgiving than a ramp profile, as the paste continues to soften and yield (hot slump) before reaching its liquidus temperature.

**Figure. 5** – Tpyical tin-lead stencil apertures. (note: inverse home plate designs are not recommend because of potential stencil or squeegee damage.

**Figure. 6**. Experimental apertures designed for lead-free paste printing.

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

The MCSB tests included both the best and worst case stencil design scenarios. In Part I, for each surface finish, paste type, profile type (ramp & soak), 300 of each device size were assembled: 1206, 0805, 0603, 0402. 150 were vertically; 150 mounted were mounted horizontally. IPC recommended pad geometries were used. 0201's were not included in the study, as many of the principles that apply to the larger passives do not necessarily translate smoothly. The authors believe that 0201's should be studied separately and in greater depth<sup>2</sup>.

In Part II, three new aperture designs were introduced. The first was a homeplate with the pointed end radiused. The second two were inverse homeplates with three corners radiused. They are illustrated in fig 6. Again, 300 of each component size were assembled, using two profiles, two surface finishes, two stencil thicknesses and two profiles

Tombstones are another common SMT defect phenomena that, like MCSB's, have many factors that influence their formation, but can be impacted by stencil design. Tombstones, also referred to as the "drawbridge effect" or "Manhattan effect," occur when the surface tension of the solder acting on one termination is greater then the surface tension on the other termination. The uneven forces create a moment on the device that causes it to rise up and stand on end like an open drawbridge. Design factors that influence tombstoning include pad geometry and thermal relief. Assembly factors that influence tombstoning include positional accuracy of the paste deposit, placement accuracy, and ramp rate entering the liquidus phase of the reflow cycle. Aperture design comes into play as it interacts with the other assembly factors: if the part is not placed on center, it is likely to contact more solder on one side of the termination than the other, which can then lead to uneven forces being applied to the component terminations as the solder melts. A typical tombstoning defect is shown in fig 7.

**Figure 7**. Tombstoning defect shows a device attached on one side while lifted up on the other side.

Historical data with tin-lead solder indicates that some aperture geometries, like the rectangle, are more forgiving in this case, but others, like homeplates, are not.

Mid-chip solder balls versus tombstones: The Balancing Act. As can be interpreted from the previous two discussions, stencil design parameters for tombstoning and mid-chip solderball appear to be exactly opposite of each other. In a real-world production a compromise must be struck. The devices used to study mid-chip solder balling were also inspected for tombstoning. Although this study was not intended to minimize tombstones, the defect rates were monitored, because the investigators did not want to optimize MCSB performance at the expense of tombstone performance.

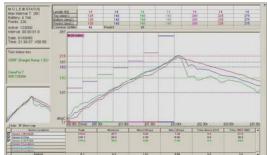

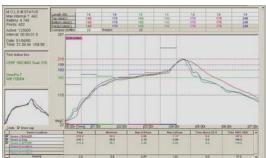

Assembly - A total of 174 circuit cards were assembled on a small, laboratory production line. The equipment set used in this study included an MPM UltraFlex 3000 stencil printer, a Universal Instruments Advantis pick and place machine, and an Electrovert OmniFlow 7-zone reflow oven with an air atmosphere. The reflow profiles are illustrated in figures 8 – 11. Solder pastes used were both Type 3, no-clean pastes. The lead-bearing alloy was Sn63/Pb37. The lead-free alloy was Sn96.5/Ag3.0/Cu0.5 (SAC 305).

**Figure 8**. Ramp profile for SnPb paste. Ramp @1.5°C/sec, Peak Temp 215°C and time above liquidus: 45 sec.

**Figure. 9.** Soak profile for SnPb paste. Soak at 160°C for 60 sec, Peak Temp 215°C and 50 sec time above liquidus.

**Figure 10**. Ramp profile for lead-free paste. Ramp @1.5°C/sec, Peak Temp 240°C and time above liquidus: 60 sec.

**Figure. 11**. Soak profile for lead-free paste. Soak at 160°C for 60 sec, Peak Temp 240°C and 60 sec time above liquidus

### **Results and Discussion**

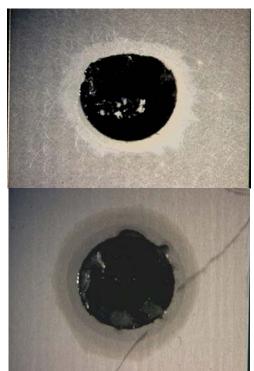

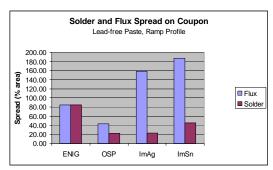

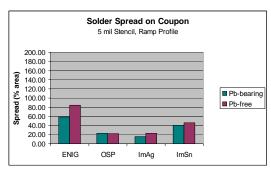

**Spread -** As described earlier, the spread test was performed in two different ways. The results are summarized in figures 12 through 14. Figures 13 and 14 show the ratio of the post-reflow deposit area to that of the printed deposit area.

**Figure. 12.** Flux and solder spread on the coupon. Upper picture is Lead-free paste spread on a pad with ImAg surface finish and lower is on ImSn finish.

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

**Figure. 13**. Shows the percentage spread on Flux and the solder on a coupon.

**Figure. 14.** Shows a comparison of the spread of the lead-free and the lead-bearing pastes on four different board finishes.

The results of this spread test show that the spread of lead-free and lead bearing pastes is very close, with lead-free spreading marginally more.

These results are quite obviously curious, as it is well documented and generally accepted that lead-bearing solders spread much better than lead-free solders. Potential reasons for this anomalous data include both the nature of the test and the measurement method. Because the printed solder sample is much smaller than the pad it is printed on the spread is not constrained by the edges of the pad. Uneven spread around the perimeter of the solder deposit is not accounted for. It's a simple area ratio calculation without consideration to form or flow of the solder. The areas are measured electronically, with human assistance in defining the measurement area. This brings a certain degree of subjectivity to the test, particularly if different people measure different specimens at different times.

The authors have harbored certain skepticism about the validity of this test method, which is why the cross-print test was introduced.

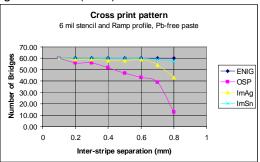

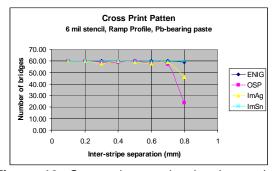

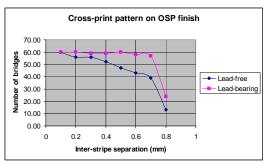

The Cross-Print test yielded much better definition in the wetting results than the simple spread tests. Figure 15 shows the number of gaps bridged for lead-free paste on all surface finishes; Figure 16 shows same results for lead-bearing paste. Figure 17 illustrates the difference in wetting by comparing both lead-bearing and lead-free paste performance on the toughest to wet (OSP) finish.

**Figure. 15.** Cross print test showing the number of bridges formed by lead-free paste printed on four different board finishes. Reflow profile used is ramp profile shown in figure 10.

**Figure. 16**. Cross print test showing the number of bridges formed by lead-free bearing printed on four different board finishes. Reflow profile used is ramp profile shown in figure 10.

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

**Figure 17.** Difference in spread of lead-free and lead-bearing pastes in OSP surface finish as observed in the cross print pattern test.

Clearly the quantified difference in spread characteristics agrees with what is known and accepted information in the industry. As anticipated ENIG finish shows complete spread even to the upper limit of the test and the ImSn showed similar behavior with only a few sites unbridged at the highest gap. Also as expected, OSP and ImAg showed lower spread characteristics with both lead-bearing and lead-free pastes.

In the future, the authors will be employing the cross-print test to characterize spread properties. In addition to improved accuracy, objectivity and resolution of this test method as compared to its predecessor, it is faster and more economical to perform.

### QFP wetting

QFPs were inspected for exposed pad material and solder bridges. A total of 348 QFPs were assembled and inspected. Only four solder bridges were found, the authors are cautious about drawing conclusions based on such a small sample size and seemingly statistically insignificant results. Because the assembly process took place in the lab environment with well tuned printing and placement equipment, the noise associated with a typical production environment was not present. The authors feel that the data will be more revealing if a larger sample size were created with the typical tolerances seen on a production equipment.

As expected ENIG and ImSn showed full spread regardless of the aperture cropping, therefore it is suggested that assemblers currently cropping

QFP aperture continue the practice when assembling onto ENIG or ImSn surface finishes.

Also as expected, OSP and ImAg did not show complete spread to the toes of the pads but both met IPC acceptability standards. ImAg did show better spread than OSP at the toes but not as good as ENIG or ImSn.

### Mid-chip Solder Balls

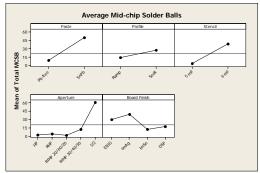

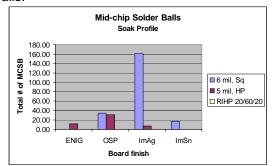

Mid-chip solder balls were counted for all the devices on the board. A total of 6,960 devices were populated and inspected. Figure. 9 summarizes total MCSB counts. Observations include:

- Lead-free paste shows less number of MCSB's than the lead-bearing paste in general.

- Immersion tin produced the least amount of MCSB's, followed by ENIG, OSP, and immersion silver.

- Soak reflow profiles produce more MCSBs than ramp profiles.

- 6 mil stencils produced far more MCSBs than 5 mil stencils. It should be noted that the 6 mil foil was designed with rectangular apertures at 1:1 with the pad, and the 5 mil foil was designed with homeplate apertures with a 10% reduction, in order to benchmark best and worst case scenarios.

**Figure 18.** Average number of mid-chip solder balls.

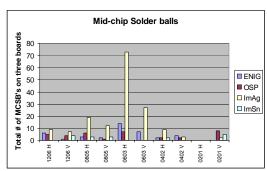

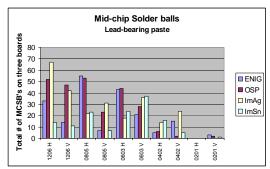

To see the breakdown by device size, the total number of MCSBs for each package type for all the four board finishes for lead-free paste in Figure 19 and for lead-bearing paste in Figure. 20. Letters H & V following the device type

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

indicate horizontally and vertically placed devices respectively. Data included here is for ramp profile. For lead-free paste there appear to be more MCSBs for the intermediate size devices (0603) especially for ImAg and ENIG board finishes. For OSP and ImSn they appear to be more evenly distributed. For lead-bearing paste the number of mid-chip solder balls observed in general decreases with the decreasing device size with only exception being the immersion silver board finish where MCSB rates appear to spike on 0603 devices. Of the 72 MCSB's recorded for immersion silver, 67 of them were observed on two assemblies that ran sequentially; one of these two boards also had 28 MCSB's on the vertically placed parts. The investigators suspect that this is anomalous data with a special cause, most likely related to placement. Nevertheless, the data was included in the final tallies and report; the reader may wish to discount this piece of data.

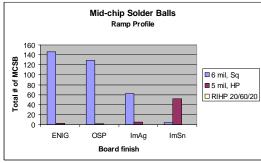

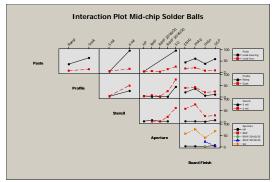

In Part II, three new apertures were studied. The radiused inverse home plate with proportions of 20%, 60%, and 20% produced the least amount of mid-chip solder balls, as seen in Figure. 20.

**Figure 19.** Mid-chip solder balls for different chip sizes and different board finishes for lead-free paste.

**Figure. 20**. Mid-chip solder balls for different chip sizes and different board finishes for lead-bearing solder paste.

**Figure 21.** Shows the total number of MCSBs for three different apertures and ramp profile. It may be noted that RIHP print data is only on OSP and ImAg finishes and produced no solder balls.

**Figure 22.** Shows the total number of MCSBs for three different apertures and soak profile.

# **Tombstoning**

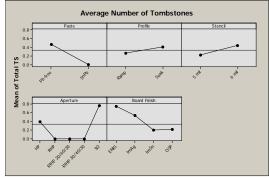

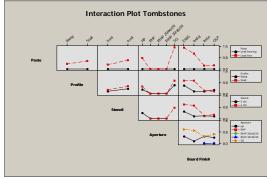

Figure 23 shows a summary of the total tombstoning defects counted on all the boards. In general the number of tombstones observed is very small. Observations include:

Lead free paste generally shows higher level of tombstoning defects as compared to lead-

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

bearing, which is most likely attributable to the better wetting behavior of the latter.

- Interestingly, the soak profile shows higher level of tombstoning defects. This contradicts some beliefs that high soak profiles can limit tombstones.

- 6 mil stencil foils produces greater amounts of tombstones than 5 mil foils, most likely due to the higher volumes of solder. The authors believe the next study should correlate printed volumes to tomsbstoning rates, and include 4 mil foils.

- The radiused inverted home plate aperture design that used the proportions 20/60/20, which was found to minimize MCSB's produced no tombstones in this study.

The authors would like to stress the fact that this test was not designed to characterize tombstoning behavior, but to ensure that aperture optimization for MCSB's did not dramatically increase tombstoning rates. The effect of placement accuracy and profile type on tombstoning is so great, that this study would have to be expanded beyond reasonable limits if it were to include placement and reflow parameters.

Figures 23-25 depict tombstone results and interaction plots for tombstones and mid-chip solder balls.

Figure 23. Average number of tombstones.

Figure 24. MCSB interaction plot

Figure 25. Tombstones interaction plot.

## **Controlling Positional Accuracy**

As stated earlier, the goal of stencil printing is to put the proper amount of solder paste in the proper location. The positional accuracy of the stencil's apertures, and the method by which they are aligned to the PWB pads, determine the location of the paste deposit. To control positional accuracy, stencil manufacturers must characterize their laser cutters and then calibrate them using offsets learned through the characterization process. One method of characterizing stencil manufacturing process is to design a standardized test vehicle, cut it, and measure the variation from CAD data, or nominal position. The test vehicle currently used for worldwide stencil calibration in Cookson Electronics is comprised of 324 identical circular apertures set on one inch centers over a 17x17 inch grid. After cutting and measuring, the data is analyzed for linear drift along the length of the machine axes and for angular displacement. The results of the analysis are then used to incorporate correction factors to ensure that

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

positional accuracy is held to 1 mil (25 m) at 4 sigma levels, or a Cpk of 1.33.

| Sigma<br>Level | Cpk  | PPM<br>Defective | Defects /<br>5000 Ops |

|----------------|------|------------------|-----------------------|

| 1.00           | 0.33 | 158700           | 793.5                 |

| 1.50           | 0.50 | 66800            | 334.0                 |

| 2.00           | 0.67 | 22800            | 1114.0                |

| 2.50           | 0.83 | 6200             | 31.0                  |

| 3.00           | 1.00 | 1350             | 6.8                   |

| 4.00           | 1.33 | 32               | 0.2                   |

| 4.5            | 1.50 | 3.4              | 0.0                   |

| 5.00           | 1.67 | 0.3              | 0.0                   |

| 6.00           | 2.00 | 0.001            | 0.0                   |

**Table 1.** Correlation of Process Capability to positional accuracy of +/- 1 mil (25 m). Notice that the PPM Defective is based on a static process, and does not include the 1.5 sigma shift

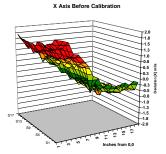

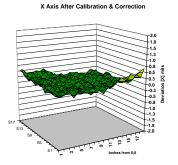

Mapping the positional accuracy of a laser cutter by measuring the finished test vehicle reveals interesting results. Figures 3 and 4 compare the X positional accuracy of a laser cutter before and after calibration. Similar shift is observed in the Y direction as well.

**Figure 25**. Positional accuracy map of Uncalibrated X-Axis.

**Figure 26.** Positional accuracy map of X Axis after Calibration

#### Aligning the Stencil and PWB

Several sources that affect the Stencil-PWB alignment variation include the variation of the positional accuracy of the PWB, the variation of the alignment capability of the printer, and the variation in the stencil itself. The PWB variation is by far the largest contributor to misalignment. PWB's are known to "shrink" from CAD data as a result of their fabrication process. They also experience some shrink in their first reflow process, exacerbating the misalignment when printing the second side of the board. To address the variation in the PWB, it can be measured so that a stencil can be generated to custom fit the PWB's.

#### **Conclusions & Recommendations**

The optimum apertures found for minimizing the formation of mid chip solder balls is the radiused inverted homeplate design with aperture proportions of 20%-60%-20%. This aperture did not produce any tombstones.

To gauge wetting and spread capability of solder pastes, the cross-print pattern was found to be superior to the spread ratio test.

QFP data was inconclusive. It is recommended that this type of test be performed in production environments to capture a greater sample size the systemic noise associated with high volume manufacturing operations.

Further studies are recommended to characterize tombstone behavior, particularly with different lead-free alloys.

### Acknowldgements

The authors wish to recognize the investigational team that performed and supported this study: Westin Bent, Grant Burkhalter, Leon Herbert, Horladine Maciel, Bawa Singh, Valentijn Van Velthoven, Greg Wade.

# References

""Reducing Variation in Outsourced SMT Manufacturing Through the use of Intelligent Stencil Systems", Chrys Shea, Valentijn Van

Published by Surface Mount Technology Association (smta.org), 5200 Willson Road, Suite 215, Edina, Minnesota 55424-1316

Velthoven, Ron Tripp and Ranjit S Pandher, To appear in Circuits Assembly 2004.

- Self-Centering of Offset Chip Components in a Pb-free Assembly", Amey Teredesai, Srinivasa Aravamudhan and Joe Belmonte, Richard Szymanowski, To be presented at IPC 2004.

- "HUPUG's Lead-free design, materials and process of high density packages", Joe Smetana, BobHorsley, John Lau, Ken Snowdon, Dongkai Shangguan, Jerry Gleason, IRV Memis, Dave Love, Walter Dauksher and Bob Sullivan, presented at IPC 2003.

- "Process characterization of pcb assembly using 0201 packages with lead-free solder, David Geiger, Fredrik Mattsson", Dr. Dongkai Shangguan, MT Ong, Patrick Wong, Mei Wang, Todd Castello, and Sammy Yi, NEPCON West - Fiberoptic Expo, 2002